Each UART contains a shift register, which is the fundamental method of. Both 74AHC595 and 74AHCT595 inputs are overvoltage tolerant. UARTs convert data between parallel and serial forms, and are widely used by. The 74AHCT595 features TTL compatible inputs. Operation of the OE input does not affect the state of the registers. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Data in the storage register appears at the output whenever the output enable input ( OE) is LOW.

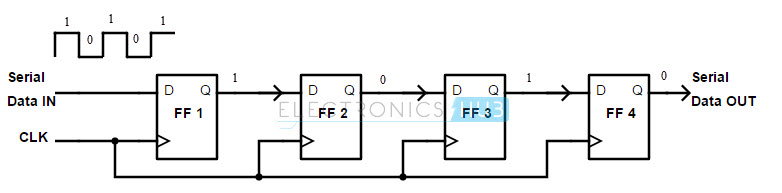

If both clocks are connected together, the shift register will always be one clock pulse ahead of the storage register. These are commonly called the SISO (Serial Input Serial Output) shift registers. The data in the shift register is transferred to the storage register on a LOW-to-HIGH transition of the STCP input. A parameterized universal shift register in Verilog what is a shift register A shift register is a very basic design element very commonly used in digital designs generally for the purposes of delaying a certain data by a certain number of clock cycles. Data is shifted on the LOW-to-HIGH transitions of the SHCP input. A LOW on MR will reset the shift register. The device features a serial input (DS) and a serial output (Q7S) to enable cascading and an asynchronous reset MR input. Both the shift and storage register have separate clocks. The following circuit is a four-bit Serial in – parallel out shift register constructed by D flip-flops.The 74AHC595 74AHCT595 is an 8-bit serial-in/serial or parallel-out shift register with a storage register and 3-state outputs.

Parallel input serial output shift register verilog code code#

VHDL code for Parallel In Parallel Out Shift Register library ieee Įnd arch Serial In – Parallel Out Shift Registersįor Serial in – parallel out shift registers, all data bits appear on the parallel outputs following the data bits enters sequentially through each flipflop. Once the register is clocked, all the data at the D inputs appear at the corresponding Q outputs simultaneously. The D’s are the parallel inputs and the Q’s are the parallel outputs. The following circuit is a four-bit parallel in – parallel out shift register constructed by D flip-flops. Parallel In – Parallel Out Shift Registersįor parallel in – parallel out shift registers, all data bits appear on the parallel outputs immediately following the simultaneous entry of the data bits. VHDL Code for shift register can be categorised in serial in serial out shift register, serial in parallel out shift register, parallel in parallel out shift register and parallel in serial out shift register. VHDL Code for Serial In Parallel Out Shift Register.

0 kommentar(er)

0 kommentar(er)